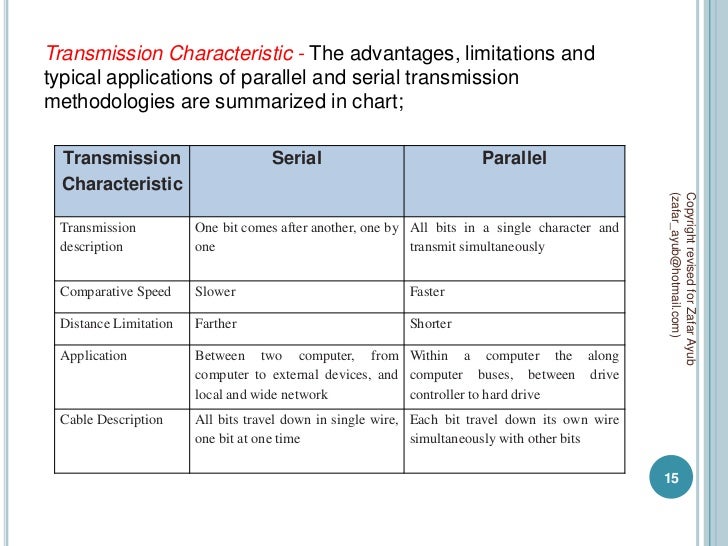

Advantages And Disadvantages Of Serial And Parallel Data Transmission

Parallel and serial data transmission are most widely used data transfer techniques. Parallel transfer have been the preferred way for transfer data. But with serial data transmission we can achieve high speed and with some other advantages. In parallel transmission n bits are transfered simultaneously, hence we have to process each bit separately and line up them in an order at the receiver. Hence we have to convert parallel to serial form. This is known as overhead in parallel transmission.

Serial Data Transmission Parallel Data transmission Advantages Disadvantages Advantages Disadvantages Used over long distances Slower to send data Faster than serial. Serial and Parallel Transmission Digital data transmission can occur in two basic modes. Data within a computer system is transmitted via parallel mode on buses with the width. Less important than the economical advantage of serial transmission. To resolve the speed and distance limitations of serial transmission via.

Signal skewing is the another problem with parallel data transmission. In the parallel communication, n bits leave at a time, but may not be received at the receiver at the same time, some may reach late than others. To overcome this problem, receiving end has to synchronize with the transmitter and must wait until all the bits are received. The greater the skew the greater the delay, if delay is increased that effects the speed.

Another problem associated with parallel transmission is crosstalk. When n wires lie parallel to each, the signal in some particular wire may get attenuated or disturbed due the induction, cross coupling etc.

As a result error grows significantly, hence extra processing is necessary at the receiver. Serial communication is full duplex where as parallel communication is half duplex. Which means that, in serial communication we can transmit and receive signal simultaneously, where as in parallel communication we can either transmit or receive the signal. Hence serial data transfer is superior to parallel data transfer. Practically in computers we can achieve 150MBPS data transfer using serial transmission where as with parallel we can go up to 133MBPS only. The advantage we get using parallel data transfer is reliability.

Serial data transfer is less reliable than parallel data transfer. How do you convert a XOR gate into a buffer and a inverter (Use only one XOR gate for each)? Implement an 2-input AND gate using a 2x1 mux.

Propisi pechatnie bukvi zhukova. Moi pervye propisi. Dorozhki i linii by Natalia Volodina and a great selection of related books, art and collectibles available now at AbeBooks.com. Obuchajuschie propisi (Paperback) Nadezhda Zhukova. Published by Eksmo (2011) ISBN 10: ISBN 13: 254. Write something about yourself. No need to be fancy, just an overview. No Archives Categories. Rabochaja tetrad 'Azbuka-propisi' soderzhit spetsialnye serii igrovykh uprazhnenij, kotorye pomogajut detjam zapomnit bukvy i vposledstvii s uspekhom ovladet navykami chtenija. Javljaetsja samostojatelnym posobiem, a takzhe dopolneniem k ljubym drugim propisjam.

What is a multiplexer? A multiplexer is a combinational circuit which selects one of many input signals and directs to the only output. What is a ring counter? A ring counter is a type of counter composed of a circular shift register.

The output of the last shift register is fed to the input of the first register. For example, in a 4-register counter, with initial register values of 1100, the repeating pattern is: 1100, 0110, 0011, 1001, 1100, so on. Compare and Contrast Synchronous and Asynchronous reset. Synchronous reset logic will synthesize to smaller flip-flops, particularly if the reset is gated with the logic generating the d-input.

But in such a case, the combinational logic gate count grows, so the overall gate count savings may not be that significant. The clock works as a filter for small reset gl. >> >> >> >> In Verilog HDL a module can be defined using various levels of abstraction. There are four levels of abstraction in verilog. They are: Behavioral or algorithmic level: This is the highest level of abstraction. A module can be implemented in terms of the design algorithm.

The designer no need to have any knowledge of hardware implementation.Data flow level: In this level the module is designed by specifying the data flow. Designer must how data flows between various registers of the design.Gate level: The module is implemented in terms of logic gates and interconnections between these gates. Designer should know the gate-level diagram of the design.Switch level: This is the lowest level of abstraction. The design is implemented using switches/transistors.

Designer requires the knowledge of switch-level implementation details. Gate-level modeling is virtually the lowest-level of abstraction, because t.

A Reset is required to initialize a hardware design for system operation and to force an ASIC into a known state for simulation. A reset simply changes the state of the device/design/ASIC to a user/designer defined state. There are two types of reset, what are they?

As you can guess them, they are Synchronous reset and Asynchronous reset. Synchronous Reset A synchronous reset signal will only affect or reset the state of the flip-flop on the active edge of the clock. The reset signal is applied as is any other input to the state machine. Advantages: The advantage to this type of topology is that the reset presented to all functional flip-flops is fully synchronous to the clock and will always meet the reset recovery time.Synchronous reset logic will synthesize to smaller flip-flops, particularly if the reset is gated with the logic generating the d-input. But in such a case, the combinational logic gate count grows, so the overall gate count savings may not be that significant.